# SERVICE MANUAL

AEP Model UK Model

#### SPECIFICATIONS

Memory

512K byte

Power consumption

+5V, 300 mA

Operating temperature and humidity

5\* to 35\* C (41\*F to 95\*F), 25% to 80%

Dimensions

Approx. 109 x 132 x 26.4 (w/h/d)

(4<sup>3</sup>/<sub>8</sub> x 5<sup>3</sup>/<sub>4</sub> x 1<sup>1</sup>/<sub>16</sub> inches)

Weight

Approx. 270 g (9.5 oz)

Design and specifications subject to change without notice.

Scanned and converted to PDF by HansO, 2001

## HBM-512

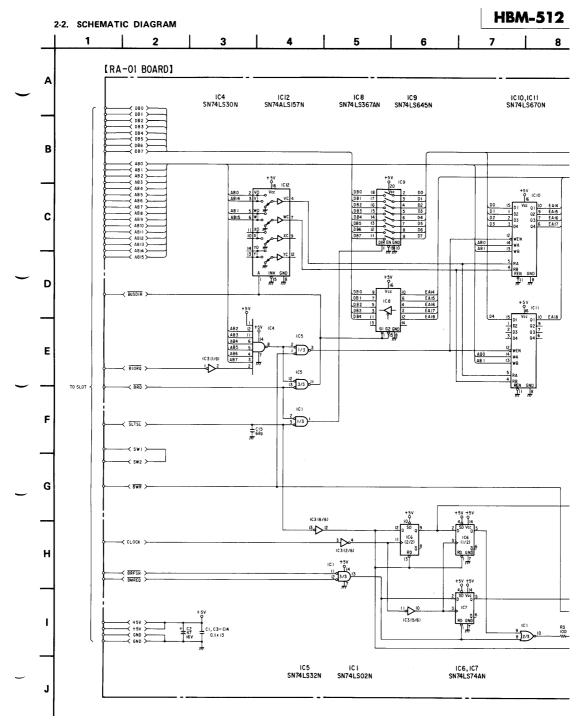

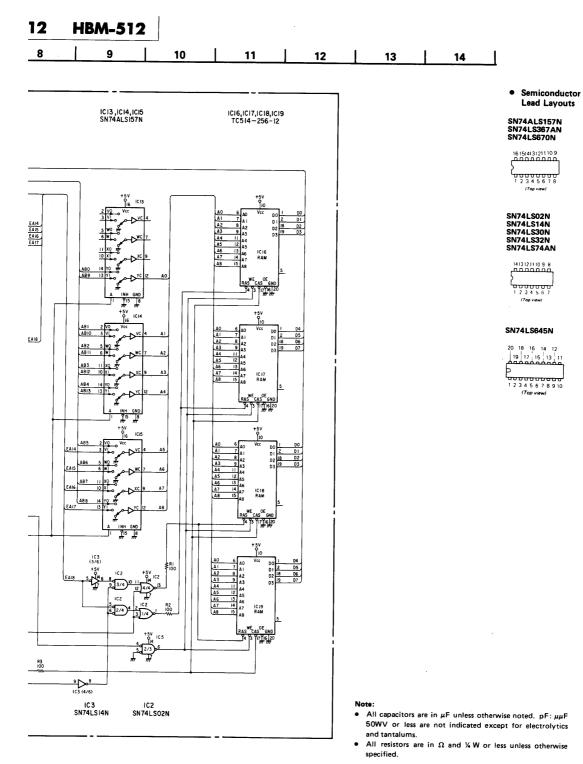

## SECTION 1 CIRCUIT DESCRIPTION

The HBM-512 is an expansion memory cartridge which is used for the HB-G900 MSX home computer. The RAM capacity is 512 k byts, as indicated by model name "512". The memory capacity of 512 kbytes is obtained by RAM chips IC16 through IC19. When using an exclusive program, this enables the expansion memory cartridge to be used as a large file which is almost the same as one floppy disk (512 k bytes). The RAM package can be used as a highspeed file because there is no mechanical access.

#### • RAM TC514-256-12

TC-514-256-12 has a memory capacity of 256 k x 4 bits and a high-speed access time of 120 nsec, as indicated by model names "256" and "-12". This RAM chip has four-bit (half-byte) data buses, and two stacked TC514-256-12s are used as eight bits (one byte). The four RAMs thus provide a capacity of 512 k bytes. TC514-256-12 is also a dynamic RAM with RAS ans CAS pins. It reads addresses A0 through A8 (adaptable in the 128-k-byte range) two times, then reads addresses A0 through A17 (adaptable in the 256-k-byte range) with the address doubled.

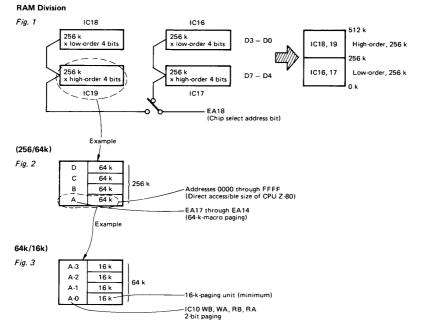

#### RAM Division

CPU Z-80 can directly handle 64 k bytes by using its own address buses (A0 through A15). However, it cannot access over 64 k bytes. Therefore, the 512-k-byte RAM is divided as shown in the figures.

As shown in the figures above, the 512-k-byte RAM area is divided into minimum paging units of 16 k bytes, and each 16-k-byte unit is divided into 512/16 = 32 pages. The RAM's minimum page is not prescribed as 64 k bytes (CPU Z-80's access range) but as 16 k bytes because 64 k bytes are divided into four pages ("0" to "3") according to the MSX specification.

-2-

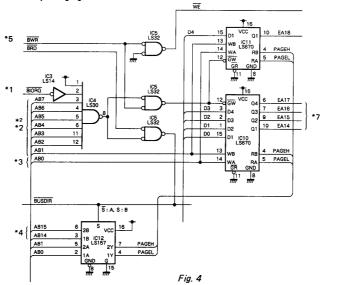

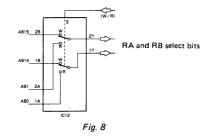

• I/O Port and 16-k-byte Paging Circuit

• Internal Configuration of IC10 and IC11 Page 0 Page 1 Page 2 Data D1 through D4 Page 3 15 D1 -1 10 - 01 Expanded address EA14 G Expanded address EA15 Expanded address EA16 Expanded address EA17 D2 G G DATA INPUTS DUTPUT D3 -2 -10 03 • THE D4 D Q G WRITE SELECT **\_**\_\_\_\_ G D G ENABLE OUTPUTS VCC DI WA WB WRITREAD 01 02 16 15 14 13 12 11 10 9 13 4 5 6 7 8 D4 RB RA 04 03 GN 2 12 13 Q4 Q3 OUTPUTS D2 G WE GR R DATA READ RITE READ INPUT INPU Fig. 6 Fig. 5 -3-

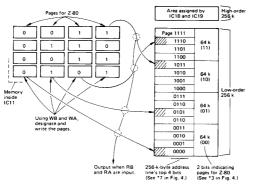

#### 16-k-byte Paging

When a pair of 256-k-byte RAMs is divided into 16-k-byte units, 256k/16k = 16 pages are obtained. In other words, the 256-k-byte RAM is divided into pages 0 through 15, arbitrary pages are picked up, and a continuous area of 64 k bytes is then formed. When the 64-k-byte area is formed, no overlapped page is used.

Fig. 7

As shown in Fig. 7, four arbitrary 16-k-byte areas are designated from the 256-k-byte RAM to make an access as a 64-k-byte RAM.

CPU Z-80 writes XXXX0000 into I/O port FC. CPU-Z-80 writes XXXX0101 into I/O port FD. CPU Z-80 writes XXXX1110 into I/O port FE. CPU Z-80 writes XXXX1011 into I/O port FF.

At that time, the page number obtained when the 256 k bytes are divided by 16 is memorized in IC11 as shown in Fig. 7. This allows access to be mapped.

The above operation is done using the following:

I/O PORT: \*1 (BIORQ) FC PORT: \*2 (111111) and \*3 (00) WRITE: \*5 (BWR)

DATA BUS XXXX0000

Next, assume that CPU Z-80 writes "FF" into address 0002 (16). Address 0002 (16) is represented as 0000 0000 0000 0010 by an address bit. For a 16-k-byte page, for example, the address is represented by 14 bits (A13 through A0). This is based on the following:

16 bits (A15 through A0) = 64 k bytes 64 k bytes/4 = 16 k bytes

64 k bytes/4 – 16 k bytes

\* Four can be represented in hexadecimal notation by two bits.

IC12 (LS157) is thus used, and the A14 and A15 signals (indicated by \*4) are input to the PAGE select circuit as shown in Fig. 4. As a result, CPU Z-80 writes data by judging that 64 k bytes are divided into arbitrary 16-k-byte units. Any one of 16-k-byte pages 0 through F is actually substituted according to the signal output from IC11.

When "FF" is written into address 0002 (16), the "FF" is written into the third byte of 256-k-byte RAM's page 0000. Therefore, the area of 64 k bytes from the CPU can be freely set in 256 k bytes.

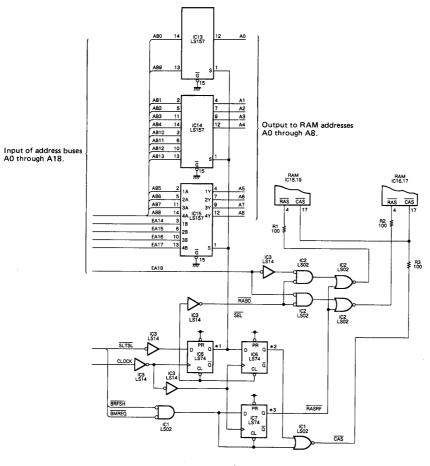

#### • COLUMN/ROW (RAS, CAS) Select Circuit

Address buses A0 through A18 are provided for the RAM. The 19 address inputs are sent to AB0 through AB13 and EA14 through EA17. The select circuit used to send the output from AB0 through AB13 and EA14 through EA17 to RAM addresses A0 through A8 as COLUMN/ROW addresses is shown in Fig. 9.

The CPU generates addresses, and an SLTSL signal selects the cartridge. At that time, the ROW addresses are being determined.

First, assume that the EA18 signal for RAM chip selection is ignored. The  $\overline{SLTSL}$  signal is passed through inverters two times. It then becomes an  $\overline{RASO}$  signal and is sent to the  $\overline{RAS}$  terminal.

The  $\overline{SEL}$  signals at pin 1 of IC13, IC14, and IC15 are low at the trailing edge of the  $\overline{RAS}$  signal. Therefore, the Y terminal of IC13, IC14, and IC15 is connected to AB0 through AB8' (ROW). The ROW addresses are sent to RAM.

When the clock goes from low to high during the positive period, Q (indicated by \*1) of flip-flop IC6 (the SEL signal) goes high. The Y terminals of IC13, IC14, and IC15 are then set to the COLUMN position of AB9 through EA17.

When the  $\overline{SEL}$  signals of IC13, IC14, and IC15 go high, the data is sent to the flip-flop (indicated by \*2) at the trailing edge of the next clock pulse.

-4-

Fig. 9

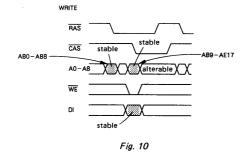

When the refresh is not ignored, the output  $\overline{(CAS)}$  of IC1 goes low (that is, COLUMN period). The

COLUMN address is memorized on the RAM during the COLUMN period. This operation is shown in Fig. 10.

EA18 is used to divide the RAM into two groups, upper and lower.

A  $\overline{BRFSH}$  (buffered refresh) signal is generated at intervals of a few milliseconds to refresh and read the RAM. The resultant signal is branched into two routes and mixed with RAS and CAS signals.

#### • IC9

This is a bidirectional buffer for data bus. The description is omitted.

-5-

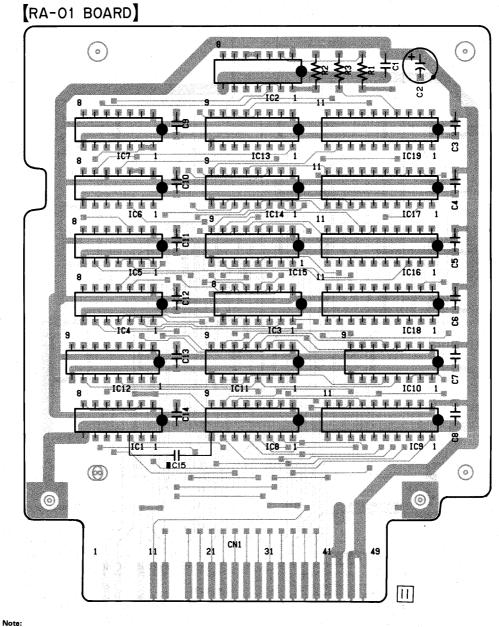

## SECTION 2 DIAGRAMS

2-1. MOUNTING DIAGRAM

is component-side pattern.

**—6**—°\*

-7-

-8-

## HBM-512

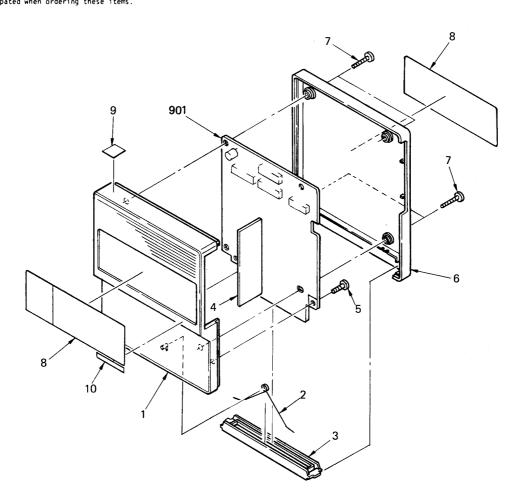

### **SECTION 3**

### EXPLODED VIEWS AND PARTS LIST

- NOTE: The mechanical parts with no reference number in the exploded views are not supplied.

- Items marked " \* " are not stocked since they are seldom required for routine service. Some delay should be antici-pated when ordering these items.

The construction parts of an assembled part are indicated with a collation number in the remark column.

| No.                        | Part No.                                                      | Description | Remarks | <u>No.</u>               | Part No.                                      | Description                                                                                                              | Remarks |

|----------------------------|---------------------------------------------------------------|-------------|---------|--------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------|

| 1<br>2<br>3<br>4<br>5<br>6 | 4-606-568-01<br>4-606-567-02<br>*4-612-050-01<br>7-685-133-19 |             |         | 7<br>8<br>9<br>10<br>901 | *4-612-062-01<br>3-703-713-01<br>3-701-690-00 | SCREW +BTP 2.6X12 TYPE2 N-S<br>LABEL, CARTRIDGE<br>STICKER, SONY SYMBOL (10)<br>LABEL (MADE IN JAPAN)<br>PC BOARD, RA-O1 |         |

-9-

## **SERVICE MANUAL**

AEP Model UK Model No. 1

## **SUPPLEMENT**

File this supplement with the service manual.

- Add the following component to the electrical parts list (page 10) and the semiconductor lead layouts (page 8) on the service manual.

- 1) Electrical Parts List (Page 10)

IC TC514256P-12 IC16-19 8-759-209-01

2) Semiconductor Lead Layouts (Page 8)

SN74LS645N TC514256P-12 20 18 16 14 12 19 17 15 13 11

(Top view)

ACC

9-952-720-81

**Sony Corporation** Áudio Group

English 87E0537-1 Printed in Japan © 1987.5